开发板是DE0,搭载Cyclone3

用的还是之前的那块ADDA板,说实话这个DAC(AD9762)似乎不适合用来射频?这个DAC标称125MSPS的刷新率,所以载波理论上只能到62.5MHz,其实调幅的话也是够用的,然而我接收用的RTLSDR最低只能到25MHz,只能给DAC超频到200MHz,然后用DDS产生30MHz的载波。

AM调制

最常听说的两种调制方法就是AM调制和FM调制,感觉现在AM调制的广播电台都很少了。

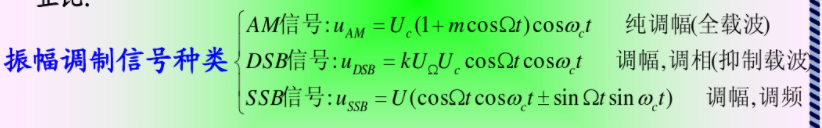

AM调制一句话描述就是让高频载波信号的幅度随音频信号的幅度变化。时域上的计算是这样:

y(t) = Asin(w_0t)*B(cos(w_1t) + 1)这是调制单一频率的音频,实际音频也是不同频率正弦波的集合。

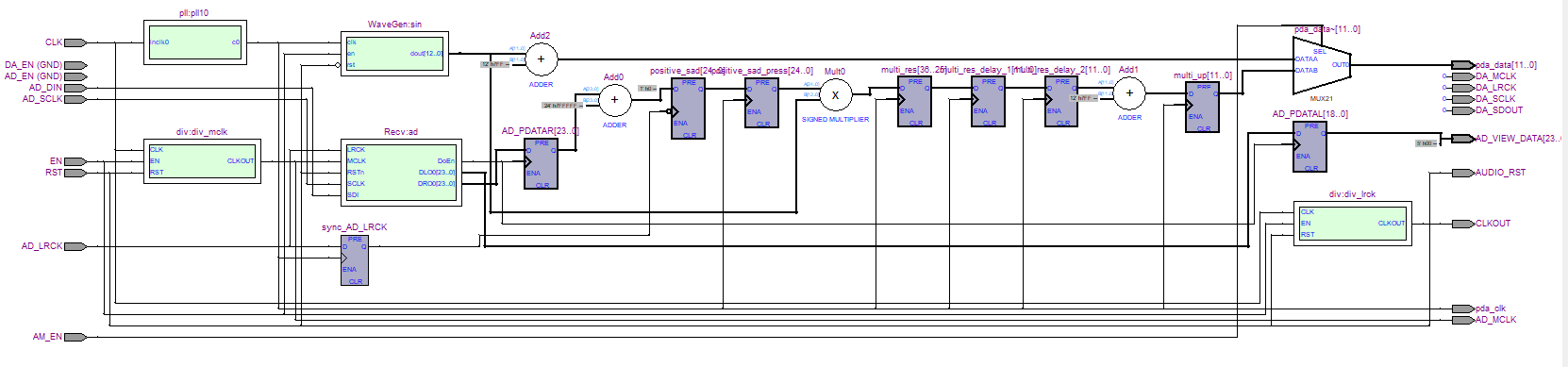

DDS和音频AD

DDS

首先需要一个高频的正弦信号作为载波,在FPGA上,自然使用DDS来产生载波信号。DDS的优势是可以灵活改变载波频率,当然这里AM调制的话,载波频率可以直接预置一个值。我用来接收的RTL23832uSDR最低只能收到25MHz,而FPGA系统时钟频率为200MHz,我选择30MHz作为载波频率。

音频AD

这里为了省事就直接使用一个音频AD,采集电脑播放的音乐

实际上这个RTL是有问题的,这个电路实际上执行的是

y(t) = A(sin(w_0t)+1)*B(cos(w_1t) + 1)得

y(t) = ABsin(w_0t)cos(w_1t) + ABcos(w_1t) + ABsin(w_0t) + AB最后调制出的结果比正确的AM调制多了一个音频信号分量和一个直流分量,实际上在发射出去的时候,这两个多出来的分量可以认为会直接消失,所以最终的发射效果并无区别。

实际上我觉得FPGA上AM调制比FM调制要烦一点的,因为不得不用到乘法器,其实我用的FPGA芯片CycloneIII虽然挺老的了,实际测试下来,200MHz的主时钟下乘法器还是比较稳定的。

就算乘法器比较慢,也可以用多个乘法器并联去构成一个流水线,给每个乘法保留出计算时间。

然后是数制问题,AD9762的输入是无符号数,但是我采样用的串行音频AD的输出是24位有符号的补码。标准的AM调制应该先给调制信号加个直流,然后再乘载波的数值。所以后面乘的时候应该用有符号乘法器,所以给调制信号加直流的时候要留个符号位。

接收到的信号的音质挺糟糕的,AM调制的载波功率很大,靠太近SDR会过载。所以只有在某个距离,甚至某种角度下,才能收到噪声比较小的信号。