一、设计目的

本设计基于网络分析仪的工作原理,借鉴开源的简易矢量网络分析仪的软硬件方案,进行优化和裁剪,设计制作基于STM32F103的简易射频阻抗检测装置。

二、设计原理

2.1 矢量网络分析的基本原理

为了使整个通信系统系统能更高效率地传送、发射或接收射频功率,通信系统中的所有组件,如传输线、天线和放大器等器件必须对信号源呈现良好的阻抗匹配。当两个连接之间的输入与输出阻抗的实部与虚部都达不到理想的状态时,便出现阻抗失配[1]。

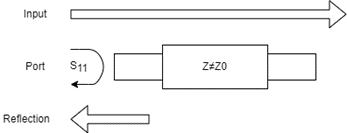

矢量网络分析仪能够测量端口的输入特性到其他端口的转移特性。NanoVNA是一个开源的微型矢量网络分析仪实现,作者为edy555。本项目以NanoVNA的软硬件设计为基础做了优化和裁剪,只保留了对S11的测量(图2.1-2)。

2.1.1 阻抗匹配原理

阻抗匹配是在设计电器负载阻抗时需要考虑的如何使信号传递功率最大化的方法。源端和负载端取得相匹配阻抗的条件是二者阻抗呈复共轭:

$$ Z_s=Z_L^* \\\ Z_s 表示源端阻抗,Z_L^* 表示负载端阻抗 $$2.1.2 阻抗测量原理

负载端和源端的阻抗关系,可以由入射波和反射波间的关系得出。反射信号的量值由瞬态阻抗的变化量决定,设源端的阻抗为Z_S,负载端的阻抗为Z_L,则反射信号与输入信号的幅值之比为:

$$ Γ=\frac{V_{reflected}}{V_{incident}} = \frac{Z_L-Z_S}{Z_L+Z_s} $$$\Gamma$ 即为反射系数,是反射信号与入射信号之比。因此可以通过测量反射信号与入射信号之比,在已知源端阻抗的前提下,就能求得负载端的阻抗。

2.1.3 史密斯圆图的阻抗表示方法

在得到负载端的阻抗后,需要将阻抗值绘制再史密斯圆图上,以便得到直观的结果。

反射系数是反射信号与入射信号之比,复阻抗与反射系数两者之间有一一对应的关系,将复阻抗平面的正时半部分映射到极坐标显示上,就形成了斯密斯圆图。

2.2 设计原理

2.2.1 混频原理

矢量网络分析仪发射一定频率的入射波,根据入射波和反射波电压或电流的幅值之比来求出器件的阻值。在本项目的电路设计中,为了提高采样精度选择了音频ADC,音频ADC采样的带宽仅有20KHz。为了避免奈奎斯特失真,ADC采样的信号不能大于10KHz。因此就需要将不同频率的入射波和反射波都通过频谱搬移的方法将频率降至10KHz以内。

假设发射的入射波是一个正弦信号,频率为$f_1$:

$$ y_{incident} (t)=Asin(2πf_1 t) $$不同特性的负载,引起不同的反射信号,反设信号假设反射信号的幅度为$B$ ,相位变化为$\phi$:

$$ y_{reflected} (t)=Bsin(2πf_1 t+ \phi) $$为了将幅度和相位信息带至较低的频率 $f_i$ 供ADC采集,使用一个频率 $f_2=f_1-f_i$ 的正弦波信号 $y_{lo} (t)=sin(2πf_2 t)$ 波信号和反射波信号相乘:

$$ \begin{aligned} y_{incident}(t) * y_{lo}(t) &= A\sin(2\pi f_1 t)\sin(2\pi f_2 t) \\\ &= \frac{A}{2}\\{-\cos[2\pi t(f_1 + f_2)] + \cos[2\pi t(f_1 - f_2)]\\} \\\ &= \frac{A}{2}\\{-\cos[2\pi t(f_1 + f_2)] + \cos[2\pi t(2\pi f_i)]\\} \end{aligned} $$$$ \begin{aligned} y_{reflect}(t) * y_{lo}(t) &= B\sin(2\pi f_1 t + \phi)\sin(2\pi f_2 t) \\\ &= \frac{B}{2}\\{\cos[2\pi t(f_1 + f_2) + \phi] - \cos[2\pi t(f_1 - f_2) + \phi]\\} \\\ &= \frac{B}{2}\\{\cos[2\pi t(f_1 + f_2) + \phi] - \cos[2\pi t(2\pi f_i) + \phi]\\} \end{aligned} $$

其中的高频信号$cos[2\pi t(f_1+f_2 )]$和$cos[2\pi(f_1+f_2 )t+\phi]$,可以使用低通滤波器滤除,最终可以在将原信号变频至较低频率的同时保留幅度和相位信息:

$$ \begin{aligned} y_{incident}^{'} &= \frac{A}{2} cos(2\pi f_i ) \\\ y_{reflected}^{'} &= \frac{B}{2} cos(2\pi f_i+\phi) \end{aligned} $$将二者经过傅里叶变换后取比值,即可得到幅度之比和相位差:

$$ \begin{aligned} Y_{incident} (w) &=\frac{A}{2} \pi[\delta(w+w_i ) + \delta(w-w_i )] \\\ Y_{reflected} (w) &=\frac{B}{2}\pi[\delta(w+w_i ) + \delta(w-w_i )] e^(j \phi/w_i ) \\\ &Γ = \frac{Y_{incident} (w)}{Y_{reflected} (w)}=\frac{A}{B} e^{-j \frac{\phi}{w_i}} \end{aligned} $$2.2.2 电阻网络定向耦合器原理

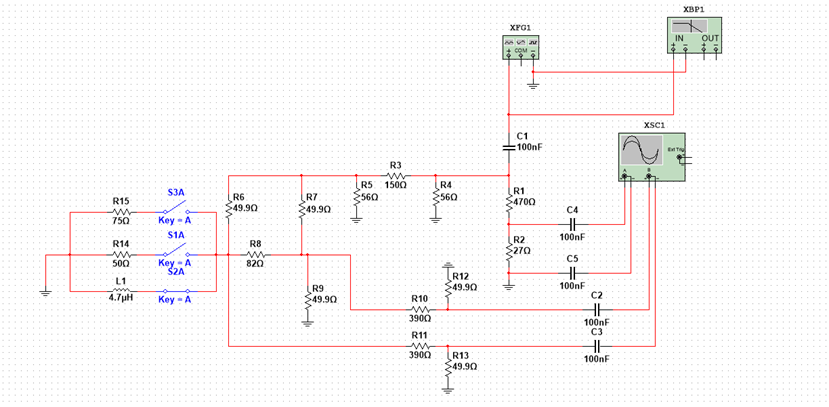

参考开源项目NanoVNA提供的原理图,设计了如下的电阻网络作为定向耦合器,分离入射波与反射波:

使用电阻网络分析方法,对上述电路进行简化(如图2.2.2.-2)后分析得到两个检测点之间的关系。

三、项目设计

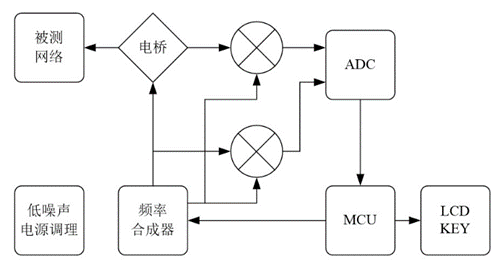

根据前文所述的测量原理,本课题设计的电路单元模块构成框图如下:

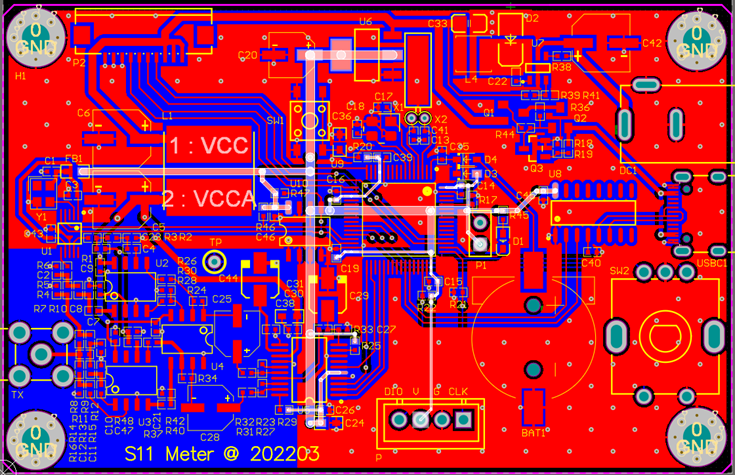

3.2 硬件设计

3.1.1 器件选型

本项目中用到的主要器件如下表:

| 序号 | 主要功能 | 型号 |

|---|---|---|

| 1 | 微控制器 | STM32F103RCT6 |

| 2 | 双平衡混频器 | SA612AD |

| 3 | 频率发生器 | Si5351A |

| 4 | 音频ADC | WM8782 |

| 5 | 26MHz温补晶振 | DSB321SDA 26MHz TCXO |

| 6 | EEPROM | 24C02 |

| 7 | USB转串口芯片 | CH340C |

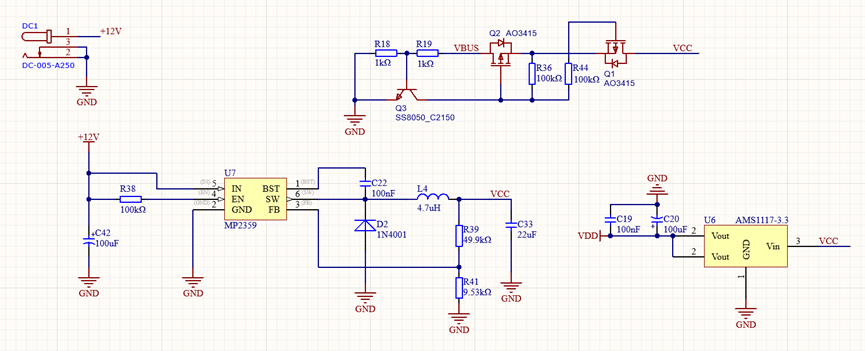

3.1.2 电源设计

本项目支持6~18V DC电源输入和5V USB电源输入,可适用多种供电场合。各类器件用到的电压为3.3V和5V两种,12V电压降为5V作为主电源,再由5V电压转换为3.3V电压,并对5V主电源进行$\Pi$型LC滤波,获得相对干净的模拟5V电源。

使用MP2339作为12V至5V电压转换器,AMS1117作为5V转3.3V电压稳压器,分别为板上器件提供5V和3.3V电源。

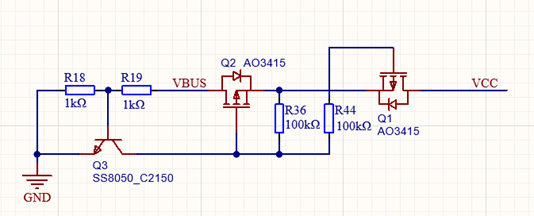

为了防止12V电源和5V电源同时连接时发生电流倒灌,在DC电源与USB电源之间设置了由Q1~Q3等构成的防倒灌电路,保证当DC电源接入时,DC电源电压不会出现在USB端。

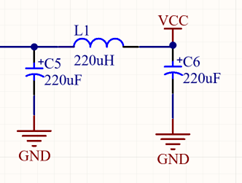

主要模拟器件有混频器SA612AD和运算放大器MC33202,在5V VCC供电前加入滤波电路,去除电源纹波和其他器件噪声的影响。

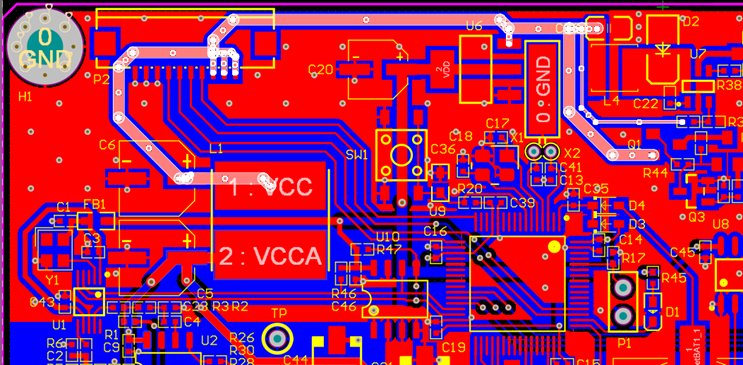

PCB上电源结构采用星型布线。

由AMS1117稳压得到的3.3V供电以ADC为中心,向左分支为Si5351和温补晶振供电,向右分支为MCU和CH340C供电,向下延伸为ADC的数字电源供电,同时切割模拟部分与数字部分的接地面。

3.1.3 扩展接口设计

在PCB上,将MCU的USART2和USART3连接到一个FPC插座,预留了两个串口传输通道作为扩展接口。例如,扩展接口可以与串口屏相连,以提供图形显示功能;或连接至天线调谐装置,自动对天线进行调谐操作。

3.1.4 模拟电路设计

Si5351产生两路输出,一路作为射频激励,传输至天线产生反射回波,两个SA612AD分别作为输入参考端和回波测量端;另一路用于混频器混频。

SA612AD产生的平衡信号经过运算放大器电路转为单端输出。测量信号和参考信号分别输入至音频ADC的左、右两声道。

3.1.5 MCU部分设计

-

STM32F103,采用8MHz晶振输入。

-

使用CH340C作为串口转USB芯片。

-

使用一个旋转编码开关。

-

一个白光LED连接在GPIO口,用作设备状态指示灯。

-

24C02 EEPROM,和Si5351连接在I2S2接口上。

-

预留了SWD调试接口,供软件开发调试使用。

3.2 软件设计

3.2.1 STM32 工程配置

使用STM32CubeIDE作为开发环境,主要使用HAL库完成程序的构建。

3.2.1-1 STM32CubeIDE工程结构

3.2.2 STM32 I2S接口的使用

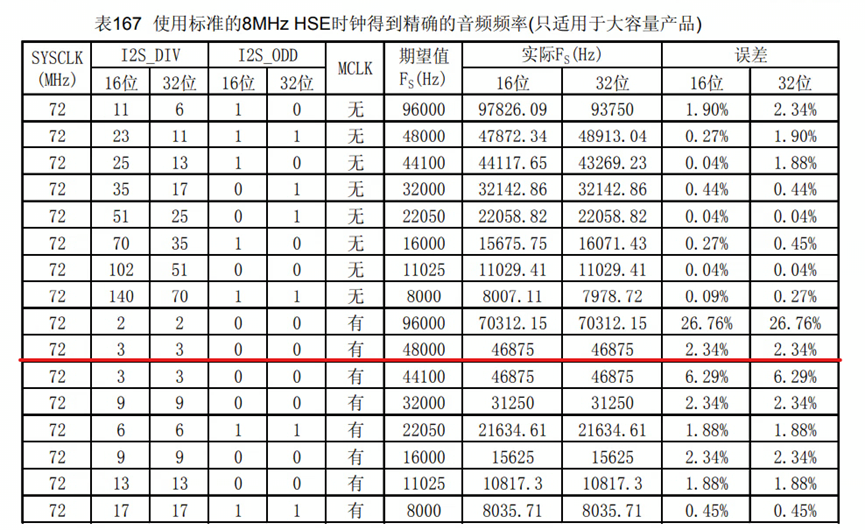

由于STM32F103最大系统时钟为72MHz,因此I2S接口最大能支持的采样频率为48kHz。I2S的时钟源是系统时钟,实际输出的主时钟MCLK频率为12.288MHz的近似值,采样频率亦是48kHz的近似值。STM32F10xxx系列参考手册中给出了不同配置下的实际采样频率值:

图3.2.2-1 STM32F103 8MHz时钟下音频频率表

根据本项目使用的晶振频率(8MHz)和系统时钟配置(72MHz),可知48kHz采样频率的配置下,实际的采样频率为46875Hz。

在实际测试中发现,SMT32 HAL库提供的I2S接收函数中并没有区分左右声道,在开启一次接收时,第一个收到的数据的声道来源是随机的。左、右声道的标志位CHSIDE位于状态寄存器SPI_SR的第三个bit处。

当配置为接收模式时,只要接收到一个音频帧,RXNE位就被置位,从数据寄存器SPI_DR中读取一次值之后,RXNE位会自动清零。CHSIDE是声道选择状态,CHSIDE=1表明收到的数据来自右声道,CHSIDE=0表明收到的数据来自左声道。

以下是阻塞读取I2S数据的读取方式:

-

在进入接收状态后,循环检查RXNE位状态直至超时。

-

发现RXNE位被置位后,读取CHSIDE位,获得声道选择信息。

-

将数据寄存器SPI_SD读取到内存中。

-

重复以上步骤直至读取到足够的数据。

为了避免抖动,引入触发机制,在真正开始连续的读取前,等待某个固定信号变化(如经过零点)到来后,再启动一次连续读取。选择稳定的参考端的输入(右声道)作为触发源。

另外,SPI_DR寄存器存储的实际上是有符号整数,但在HAL库中被定义为了无符号整数,因此在转换至浮点数进行计算前,必须要先转换为有符号整数。

等待ADC采集信号占据了测量的主要时间,如果每次采样长度为512点,则每个频点上的采样至少要花费(1/48000)*512=0.01067s。相对于STM32F103的72MHz系统时钟,48kHz的采样频率是非常慢的,为了避免因为采样过程中的阻塞等待而浪费时间,需要充分利用采样间隔。

我们用一种比较简单的思路实现了上述目的。首先使用DMA进行I2S接收,在开启DMA接收后,不断检查DMA控制器的计数器,当发现有新增的尚未处理的采样值时,就调用处理函数对其逐一处理。使用DMA的目的是为了灵活地插入其他操作,即使操作耗时超越了采样的间隔时间,或者被中断打断,也不会影响数据的连续和完整。

3.2.3 STM32 I2C接口的配置

Si5351默认的I2C地址为0x60,EEPROM 23C02N的默认地址为0xA0,在二者不冲突前提下,不修改它们的默认地址。

STM32F103RCT6的I2C2端口与I2S2端口存在冲突,在本项目中无法使用STM32自带的I2C外设,另外ST公司为了规避I2C的版权问题,将I2C设计得比较复杂,在STM32F1系列器件上稳定性不佳,因此本设计选择软件模拟I2C的方式控制Si5351。

3.2.4 Si5351频率控制

Si5351可以产生任意频率,用作本项目中的信号发生器。

Si5351A具有两个PPL,PPLA和PPLB。每个PPL都可以单独晶振、CMOS时钟输入作为是时钟源,本项目选用的Si5351A 10-MOSP型号只有晶振输入。每个时钟输出都可以选着任意PLL输出作为自己的输入。

Si5351内部具有三个频率合成阶段。第一阶段,PLL的压控振荡器使用Multisynth技术产生700~900MHz的中间频率;第二阶段,对应每个时钟输出都有一个Multisynth分频器,将阶段一产生的中间频率分频至500kHz到200MHz;在输出阶段,有一个R分频器可以继续分频至最低2.5kHz。

这里借鉴了开源硬件NanoVNA的开源代码和RFzeroTM网站上提供的Si5351寄存器计算方法[3]。

-

首先需要找到PLL合适的输出频率,压控振荡器的输出范围为700~900MHz,对于不同的目标频率,选择不同的倍频与分频方案。其中,偏好性地选择某些配置以获得更高质量的信号。

-

根据计算得到的合适的压控振荡器频率,计算出a,b,c三个参数,分别存储到MSNx_P1~MSNx_P3寄存器。

-

将计算结果按照参考手册中的寄存器地址,使用I2C接口依次写入到Si5351中。

3.2.5 DFT计算优化

得益于STM32F103对单周期乘法的支持,可以以足够快的速度在单片机内完成运DFT算。由于本设计中只需要计算中频频点上的变换值即可,并不需要求出全部的FFT。而离散傅里叶变换中,旋转因子$W_N^{nk}$是固定不变的,因此可以在设置中频频率时,提前根据中频频率$IF$、采样长度$N$和ADC采样频率$f_s$计算好旋转因子$W_N^{nk}$。

由下式可以计算出旋转因子的参数$k$

$$ k=\frac{IF×N}{f_s} +1 $$得到$k$后,由下式计算出旋转因子的实部和虚部:

$$ Real(W_N^{nk} )=\cos(2\pi\frac{nk}{N}) \\\ Imag(W_N^{nk} )=\sin(2\pi \frac{nk}{N}) $$使用ARM提供的DSP计算库,将上述计算得到的旋转因子存储为$N\times 1$的矩阵,将采样得到的数据存储为$1\times N$的矩阵,再使用DSP计算库提供的矩阵相乘函数一次计算即可得到中频频率点上的DFT值。

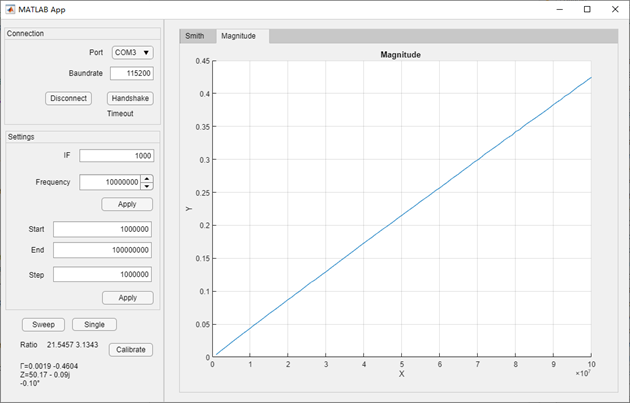

3.2.6 MATLAB App上位机软件

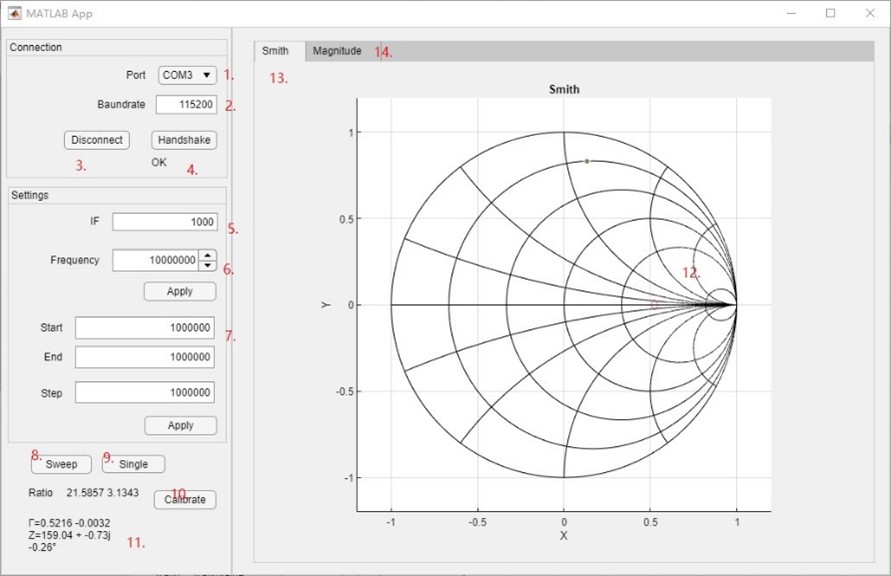

为了方便解读设备采集的信息,基于MATLAB App功能开发了上位机软件,通过串口与下位机通信,以图形化的方式将测量出的阻抗值绘制到图中。

显示界面功能按钮、参数设置以及标签说明:

- Port:选择串口端口

- Baudrate:选择串口通信的波特率

- Connect/Disconnect:控制串口的连接与断开

- Handshake:与设备握手,确保设备处在正确的工作状态。

- IF:中频频率设置。

- Frequency:单次测量的频率设置,点击下方“Apply”按钮应用设置。

- Start/End/Step:设置连续扫频的起点、终点和步进距离,点击下方“Apply”按钮应用设置。

- Sweep:进行一次连续扫频测量。

- Single:进行一次单次测量。

- Calibrate:校准按钮,当校准按钮按下时,点击“Single”按钮会更新校准值。

- 显示单次测量的测量结果,从上到下依次为回波系数、阻抗、相位延迟的测量结果。

- 显示在史密斯圆图上的阻抗点。

- 史密斯圆图选项卡。

- 幅频图选项卡。

四、项目验证

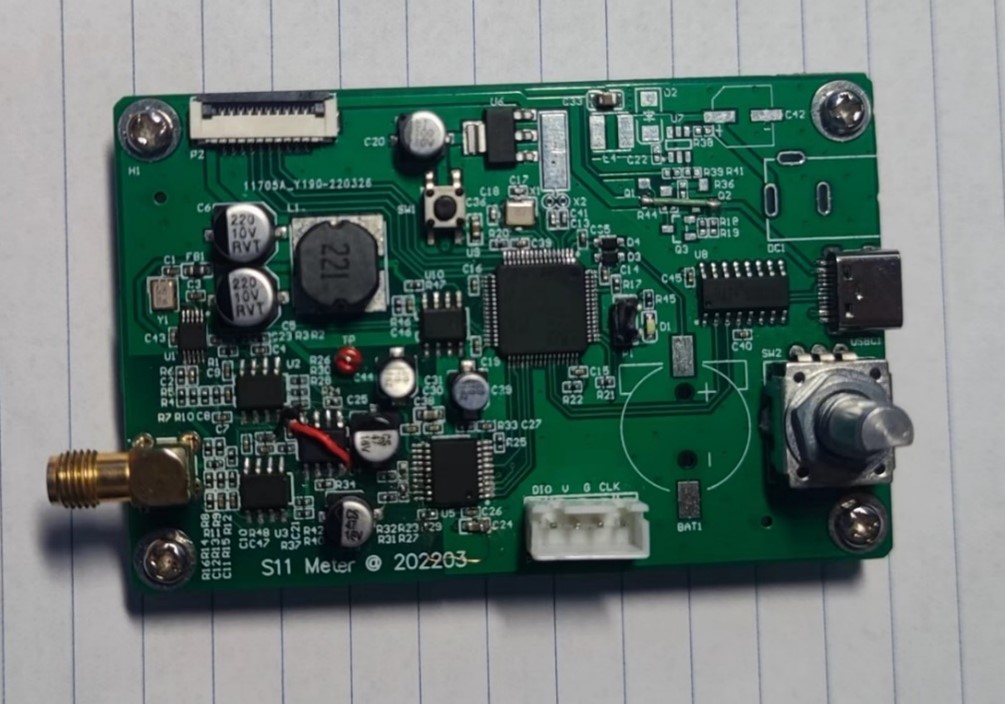

经过PCB制板和SMT贴片,得到用于测试的电路实物:

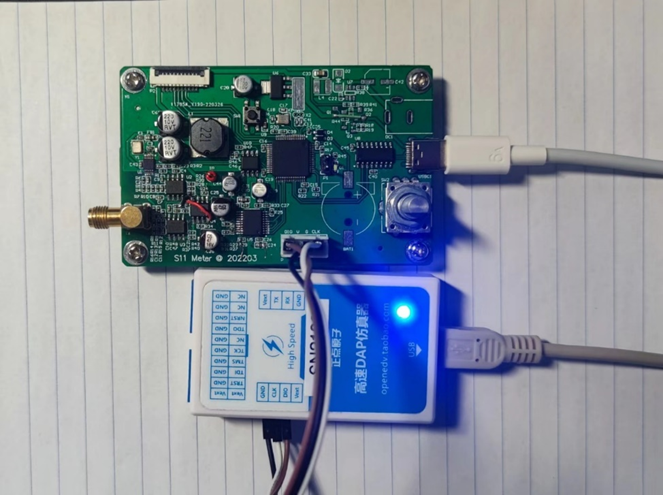

连接电源和单片机调试器:

下载测试程序到单片机中,确认单片机能正常配置:

4.1.1 混频效果

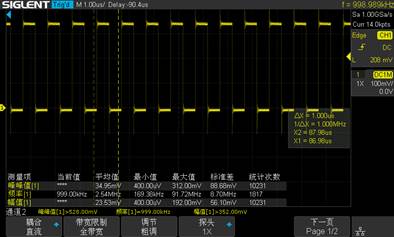

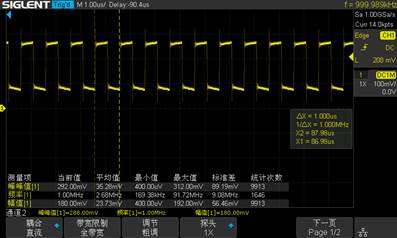

验证方式:配置Si5351的CLK2输出激励频率为1000kHz,CLK1输出混频频率999kHz,使用滤波器测量Si5351的时钟输出引脚和两个SA612AD输出引脚。

测试设备:SIGLENT SDS1102X-C示波器,100MHz,1GSa/s。

使用示波器测量Si5351的CLK1引脚:

44.1.1-1 Si5351 CLK1引脚输出波形

使用示波器测量Si5351的CLK2引脚:

图4.1.1-2 Si5351 CLK2引脚输出波形

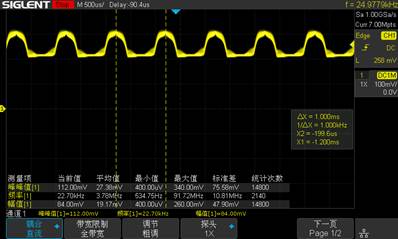

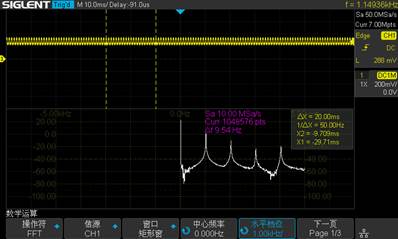

负载开路,使用示波器测量参考端SA612AD输出引脚,经游标测量和FFT分析可知,激励信号被正确地下变频到1kHz处。

图4.1.1-3 游标测量信号频率

5.1.2 低通滤波效果

音频ADC WM8782中内置了低通滤波器,下面验证低通滤波器的滤波效果。

验证方法:让负载开路,Si5351设置为与验证混频效果一节中相同的设置。在MCU中连续采集一段ADC数据,并通过串口打印出来,将打印出的数据采集到MATLAB并绘制出波形图。

可以观察到,左、右两声道信号经过滤波后,得到了比较连续平滑的结果。

4.2 设备功能验证

4.2.2 MATLAB App上位机软件测试

打开MATLAB App上位机软件,选择端口和波特率,点击“Connect”按钮连接。

将一个可变电阻器连接到终端处,点击“Single”按钮,即可测得可变电阻器的阻值。图5.2.2-5是使用万能表测量出的可变电阻器阻值,图5.2.2-6是使用单次测量功能的测量结果。

将可变电阻器调至约50欧姆,并联一个22nF的电容,使用Sweep功能测量其频率响应。首先设置扫频范围为1MHz~100MHz,步进1MHz:

图4.2.2-8 在可变电阻器上并联一个22nF电容

点击Sweep,查看连续测量得到的曲线:

在Magnitude选项卡查看幅频曲线: